IS220PDIAH1BE 336A5026ADP4 将2.5D/3D集成电路物理验证提升到新的水平

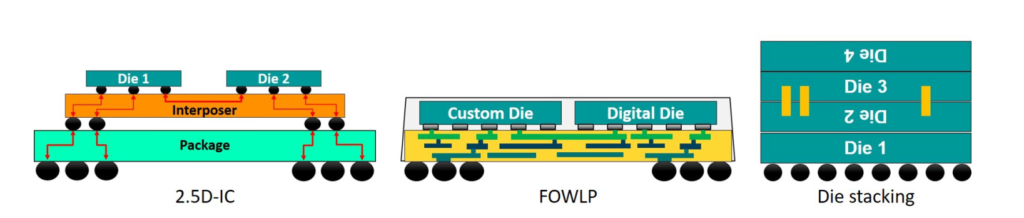

各种终端用户应用对高密度先进封装(HDAP)的采用持续增长。使用插入物(硅或有机)的2.5D集成电路(IC)设计通常以高端应用为目标,如军事、航空航天和高需求计算,而台积电集成扇出(InFO)封装等3D扇出封装方法则更侧重于手机等大规模消费电子应用。因此,主要的设计公司、代工厂和外包半导体组装和测试(OSAT)公司正在投资下一个级别——使用硅通孔(tsv)和混合焊接的真正芯片堆叠。这些HDAP设备的验证非常复杂,需要一种新的从设计到制造的模式。

HDAP技术公司

EDA工具如何实现HDAP验证?

对HDAP验证的电子设计自动化(EDA)支持随着HDAP设计的使用而发展。与HDAP核查相关的多个问题已在HDAP核查解决方案中得到解决。

例如:

- 用于封装设计的装配设计套件(adk)的开发。

- 先进封装用装配级LVS的概念和要求。

- 先进封装的布局后模拟仿真和数字静态时序分析(STA)流程。

- 在考虑芯片、封装和芯片/封装接口寄生效应的同时,生成HDAP系统级连接的选项。

- 解决3D IC验证中“数据不完整”问题的验证选项。

HDAP验证的要求是什么?

HDAP实物核查最简单的形式包括两个主要要求:

- 连通性:验证多个芯片是否通过封装/转接板布线正确连接

- 对齐:验证封装/插入器顶部的多个管芯是否按预期对齐

2.5/3D集成电路物理验证的基本定义通常被认为是完善的–这意味着最终客户和生态系统合作伙伴都知道并理解基本要求。事实上,生态系统协作是3D IC物理验证设计套件开发的驱动力,这些套件是封装adk的开端。

EDA工具验证如何跟上HDAP的发展?

随着3D IC技术的进步和设计公司构建更复杂的HDAP设计,物理验证的要求也在不断扩大。这些先进的物理验证要求将3D IC物理验证推向了新的高度。为了跟上步伐,EDA供应商正在扩展其3D IC验证工具和策略的功能。

例如:

- 设计师将需要执行签署设计规则检查(DRC)和LVS验证。

- 必须加强关键的对准检查。

- 芯片/转接板对准检查是3D IC验证过程中的一个重要步骤。

- 转接板至芯片检查中的假错误。

- 调试中心检查未对准错误。

- 中心检查文本凸起/焊盘。

您如何管理缺失或不完整的3D IC数据?

许多设计团队在3D IC验证流程中面临的挑战之一是有效管理不完整的数据和不正确的设置。

- 输入中缺少数据

- 缺少对齐检查

- 系统问题,如布局和源之间的引脚名称差异等。

为了将这些影响降至最低,必须提供一种创新的预检模式,使设计人员能够捕捉任何明显的设置/数据问题。这种预检模式有助于在签署运行之前发现任何早期系统级/多芯片集成问题。预检模式必须包括多个数据和设置问题检测流程,包括:

- 源网表检查

- 检查短信垫

- 缺失或额外端口检查

- 甲板覆盖率

- 插入器的电源和接地短路检查等。