D201134 解开3DIC左移策略:导航多维IC世界

IC设计的发展不断将摩尔定律的边界推向新的高度。近年来最有趣的发展之一是多维2.5D和3DICs的兴起。与传统ic不同,这些设计由多个独立的小芯片组成,每个小芯片都针对特定用途进行了优化。设计师面临的挑战在于有效连接这些小芯片。幸运的是,通过合并左移位 3DIC设计流程框架内的策略。

3DIC设计选项和组装流程

设计3DIC组件是一个复杂的过程,从小芯片组件开始。多维集成电路为连接小芯片提供了无数种设计选择。一些最常见的方法包括通过具有凸点连接和硅通孔(tsv)的插入物连接的小芯片、直接放置在封装上的小芯片或通过各种接合技术堆叠在彼此顶部的小芯片。在单个3DIC组件上结合这些方法的灵活性开辟了新的可能性,但也为设计人员带来了独特的挑战。

选择正确的3DIC布局是至关重要的第一步,因为它会影响热应力和机械应力,进而影响电气性能。这个决策过程通常需要多次迭代才能达到最佳设计。

3DIC物理验证的挑战

2.5/3DIC设计的物理验证(PV)为前沿领域带来了新的挑战。首先根据晶圆代工工艺节点要求验证每个小芯片,这项任务类似于验证片上系统(SoC)设计中的各个模块。然而,与传统PV的真正差异发生在装配验证期间。

对于布局与原理图(LVS)的验证,设计人员传统上使用CSV或电子表格格式的手动创建的组件网表,并需要“伪器件”平台,这很容易出现人为错误。此外,为设计规则检查(DRC)和包内不同接口的LVS使用单独的规则组可能会很麻烦且容易出错。

此外,仅依靠接口规则组实际上不可能生成理解多个组件之间电气交互所需的完整装配后布局网表,这是验证的一个关键方面。

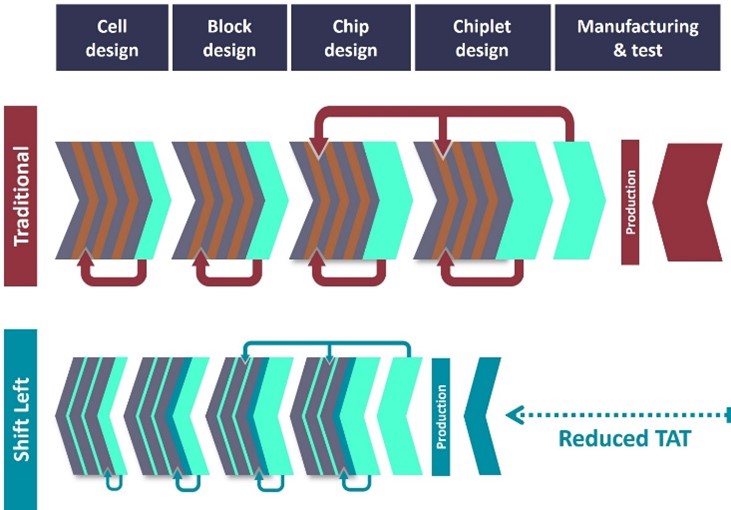

将左移验证引入3DIC设计

为了加快上市时间并实现IC设计的早期批量生产,Calibre Design Solutions提供了创新的工具和功能,使设计公司能够以Calibre签署的准确性实施早期设计阶段验证,从而提高生产率和设计质量,同时缩短上市时间。如此图所示,它既简单又有效:

_副本-364x276.png)